Produkty Kategoria

- Nadajnik FM

- 0-50w 50w-1000w 2kw-10kw 10kw +

- Nadajnik TV

- 0-50w 50-1kw 2kw-10kw

- Antena FM

- Antena telewizyjna

- antena Accessory

- Kabel Złącze Splitter zasilania Dummy obciążenia

- Tranzystor RF

- Zasilacz laboratoryjny

- Urządzenia audio

- DTV Front End Equipment

- system link

- System STL System Link mikrofalowa

- Radio FM

- power Meter

- Produkty z drewna

- Specjalnie dla koronawirusa

produkty Tagi

Miejsca Fmuser

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> Afrikaans

- sq.fmuser.net -> albański

- ar.fmuser.net -> arabski

- hy.fmuser.net -> Armeński

- az.fmuser.net -> Azerbejdżański

- eu.fmuser.net -> baskijski

- be.fmuser.net -> białoruski

- bg.fmuser.net -> bułgarski

- ca.fmuser.net -> kataloński

- zh-CN.fmuser.net -> chiński (uproszczony)

- zh-TW.fmuser.net -> chiński (tradycyjny)

- hr.fmuser.net -> chorwacki

- cs.fmuser.net -> czeski

- da.fmuser.net -> duński

- nl.fmuser.net -> holenderski

- et.fmuser.net -> estoński

- tl.fmuser.net -> filipiński

- fi.fmuser.net -> fiński

- fr.fmuser.net -> francuski

- gl.fmuser.net -> galicyjski

- ka.fmuser.net -> gruziński

- de.fmuser.net -> niemiecki

- el.fmuser.net -> grecki

- ht.fmuser.net -> kreolski haitański

- iw.fmuser.net -> hebrajski

- hi.fmuser.net -> hindi

- hu.fmuser.net -> węgierski

- is.fmuser.net -> islandzki

- id.fmuser.net -> indonezyjski

- ga.fmuser.net -> irlandzki

- it.fmuser.net -> włoski

- ja.fmuser.net -> japoński

- ko.fmuser.net -> koreański

- lv.fmuser.net -> łotewski

- lt.fmuser.net -> litewski

- mk.fmuser.net -> macedoński

- ms.fmuser.net -> malajski

- mt.fmuser.net -> maltański

- no.fmuser.net -> norweski

- fa.fmuser.net -> perski

- pl.fmuser.net -> polski

- pt.fmuser.net -> portugalski

- ro.fmuser.net -> rumuński

- ru.fmuser.net -> rosyjski

- sr.fmuser.net -> serbski

- sk.fmuser.net -> słowacki

- sl.fmuser.net -> słoweński

- es.fmuser.net -> hiszpański

- sw.fmuser.net -> suahili

- sv.fmuser.net -> szwedzki

- th.fmuser.net -> Tajski

- tr.fmuser.net -> turecki

- uk.fmuser.net -> ukraiński

- ur.fmuser.net -> Urdu

- vi.fmuser.net -> wietnamski

- cy.fmuser.net -> walijski

- yi.fmuser.net -> jidysz

Co to jest połowa sumatora: schemat obwodu i jego zastosowania

Date:2021/10/18 21:55:58 Hits:

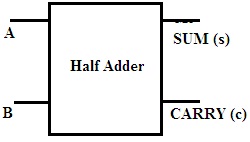

Half Adder jest rodzajem podstawowego układu cyfrowego. Wcześniej w Obwodach Analogowych wykonywane są różne operacje. Po odkryciu elektroniki cyfrowej wykonywane są w niej podobne operacje. Systemy cyfrowe są uważane za skuteczne i niezawodne. Wśród różnych operacji jedną z najważniejszych operacji jest arytmetyka. Obejmuje dodawanie, odejmowanie, mnożenie i dzielenie. Wiadomo już jednak, że może to być komputer, każdy elektroniczny gadżet, taki jak kalkulator, może wykonywać operacje matematyczne. Operacje te są wykonywane z wartości binarnych. Jest to możliwe dzięki obecności w nim pewnych obwodów. Obwody te są określane jako sumatory i odejmowania binarne. Ten typ obwodów jest przeznaczony do kodów binarnych, kodów Excess-3, a także innych kodów. Dalsze dodatki binarne są podzielone na dwa typy. Są to: Half Adder i Full Adder Co to jest Half Adder? Cyfrowy obwód elektroniczny, który wykonuje dodawanie na liczbach binarnych, jest zdefiniowany jako Half Adder. Proces dodawania jest denary, jedyną różnicą jest wybrany system liczbowy. W systemie liczb binarnych istnieje tylko 0 i 1. Waga liczby jest całkowicie oparta na pozycjach cyfr binarnych. Spośród tych 1 i 0, 1 jest traktowana jako największa cyfra, a 0 jako mniejsza. Schemat blokowy tego sumatora to Half AdderHalf Adder Circuit DiagramPołowa sumatora składa się z dwóch wejść i wytwarza dwa wyjścia. Jest uważany za najprostszy układ cyfrowy. Wejściami tego obwodu są bity, na których ma być wykonane dodawanie. Uzyskane wyniki są sumą i przeniesieniem.

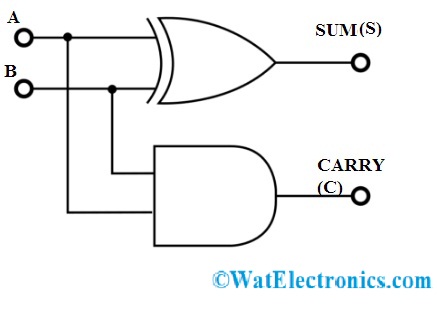

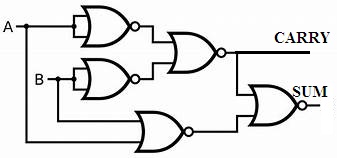

Half AdderHalf Adder Circuit DiagramPołowa sumatora składa się z dwóch wejść i wytwarza dwa wyjścia. Jest uważany za najprostszy układ cyfrowy. Wejściami tego obwodu są bity, na których ma być wykonane dodawanie. Uzyskane wyniki są sumą i przeniesieniem.  Half AdderObwód tego sumatora składa się z dwóch bramek. Są to bramki AND i XOR. Zastosowane wejścia są takie same dla obu bramek obecnych w obwodzie. Ale dane wyjściowe są pobierane z każdej bramki. Wyjście bramki XOR jest określane jako SUM, a wyjście AND jest znane.

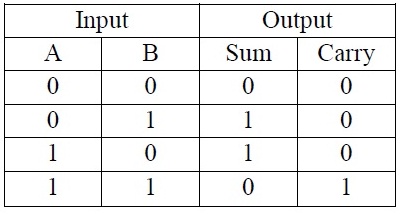

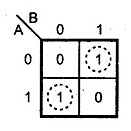

Half AdderObwód tego sumatora składa się z dwóch bramek. Są to bramki AND i XOR. Zastosowane wejścia są takie same dla obu bramek obecnych w obwodzie. Ale dane wyjściowe są pobierane z każdej bramki. Wyjście bramki XOR jest określane jako SUM, a wyjście AND jest znane. Half Adder Truth Table Z powyższej tabeli prawdy punkty są widoczne w następujący sposób: Jeśli A=0, B=0, czyli oba zastosowane wejścia mają wartość 0. Wtedy oba wyjścia SUM i CARRY mają wartość 0. Wśród dwóch zastosowanych wejść, jeśli ktoś wejście wynosi 1, to SUMA będzie równa e1, ale CARRY jest równe 0. Jeśli oba wejścia mają wartość 1, to SUMA będzie równa 0, a CARRY będzie równe 1. Na podstawie zastosowanych wejść pół sumator kontynuuje operację dodatku.RównanieRównanie dla tego typu obwodów można zrealizować za pomocą koncepcji sumy produktów (SOP) i produktów sumy (POS). Równanie Boole'owskie dla tego typu obwodów określa relację między zastosowanymi wejściami a uzyskanymi wyjściami. W celu wyznaczenia równania na podstawie wartości tabeli prawdy rysowane są k-mapy. Składa się z dwóch równań, ponieważ są w nim używane dwie bramki logiczne.K-mapa przeniesienia to

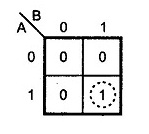

Half Adder Truth Table Z powyższej tabeli prawdy punkty są widoczne w następujący sposób: Jeśli A=0, B=0, czyli oba zastosowane wejścia mają wartość 0. Wtedy oba wyjścia SUM i CARRY mają wartość 0. Wśród dwóch zastosowanych wejść, jeśli ktoś wejście wynosi 1, to SUMA będzie równa e1, ale CARRY jest równe 0. Jeśli oba wejścia mają wartość 1, to SUMA będzie równa 0, a CARRY będzie równe 1. Na podstawie zastosowanych wejść pół sumator kontynuuje operację dodatku.RównanieRównanie dla tego typu obwodów można zrealizować za pomocą koncepcji sumy produktów (SOP) i produktów sumy (POS). Równanie Boole'owskie dla tego typu obwodów określa relację między zastosowanymi wejściami a uzyskanymi wyjściami. W celu wyznaczenia równania na podstawie wartości tabeli prawdy rysowane są k-mapy. Składa się z dwóch równań, ponieważ są w nim używane dwie bramki logiczne.K-mapa przeniesienia to  K-Map AND GateRównanie wyjściowe CARRY jest otrzymywane z bramki AND.C=A.BWyrażenie logiczne dla sumy jest realizowane przez formularz SOP. Stąd mapa K dla SUM to

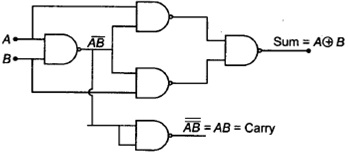

K-Map AND GateRównanie wyjściowe CARRY jest otrzymywane z bramki AND.C=A.BWyrażenie logiczne dla sumy jest realizowane przez formularz SOP. Stąd mapa K dla SUM to K-Mapa dla sumy (XOR)Wyznaczone równanie to S= A⊕ BZastosowania Zastosowania tego podstawowego sumatora są następujące: Aby wykonać dodawanie na bitach binarnych, jednostka arytmetyczna i logiczna obecna w komputerze preferuje ten obwód sumatora. do tworzenia obwodu pełnego sumatora. Te obwody logiczne są preferowane w projektowaniu kalkulatorów. Do obliczania adresów i tabel preferowane są te obwody. Zamiast tylko dodawania, obwody te są w stanie obsługiwać różne aplikacje w obwodach cyfrowych. Co więcej, staje się to sercem elektroniki cyfrowej.Kod VHDLKod VHDL dla obwodu Half Adder islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit;sum,carry:out bit);end half_adder ;dane architektoniczne half_adder isbeginsum<= a xor b;carry <= a i b;koniec danych;FAQs1. Co rozumiesz przez Adder? Obwody cyfrowe, których jedynym celem jest dodawanie, są znane jako Addery. To są główne składniki ALU. Sumatory działają oprócz różnych formatów liczb. Wyjścia sumatorów to suma i carry.2. Jakie są ograniczenia połowy sumatora? Nie można dodać bitu przeniesienia wygenerowanego z poprzedniego bitu, co jest ograniczeniem tego sumatora. Aby wykonać dodawanie wielu bitów, te obwody nie mogą być preferowane.3. Jak zaimplementować Half Adder za pomocą bramki NOR? Implementację tego typu sumatora można również wykonać za pomocą bramki NOR. To kolejna uniwersalna brama.

K-Mapa dla sumy (XOR)Wyznaczone równanie to S= A⊕ BZastosowania Zastosowania tego podstawowego sumatora są następujące: Aby wykonać dodawanie na bitach binarnych, jednostka arytmetyczna i logiczna obecna w komputerze preferuje ten obwód sumatora. do tworzenia obwodu pełnego sumatora. Te obwody logiczne są preferowane w projektowaniu kalkulatorów. Do obliczania adresów i tabel preferowane są te obwody. Zamiast tylko dodawania, obwody te są w stanie obsługiwać różne aplikacje w obwodach cyfrowych. Co więcej, staje się to sercem elektroniki cyfrowej.Kod VHDLKod VHDL dla obwodu Half Adder islibrary ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit;sum,carry:out bit);end half_adder ;dane architektoniczne half_adder isbeginsum<= a xor b;carry <= a i b;koniec danych;FAQs1. Co rozumiesz przez Adder? Obwody cyfrowe, których jedynym celem jest dodawanie, są znane jako Addery. To są główne składniki ALU. Sumatory działają oprócz różnych formatów liczb. Wyjścia sumatorów to suma i carry.2. Jakie są ograniczenia połowy sumatora? Nie można dodać bitu przeniesienia wygenerowanego z poprzedniego bitu, co jest ograniczeniem tego sumatora. Aby wykonać dodawanie wielu bitów, te obwody nie mogą być preferowane.3. Jak zaimplementować Half Adder za pomocą bramki NOR? Implementację tego typu sumatora można również wykonać za pomocą bramki NOR. To kolejna uniwersalna brama. Half Adder przy użyciu bramek NOR4. Jak zaimplementować Half Adder za pomocą bramki NAND? Bramka NAND jest jednym z rodzajów bramek uniwersalnych. Wskazuje, że każdy rodzaj projektowania obwodów jest możliwy przy użyciu bramek NAND.

Half Adder przy użyciu bramek NOR4. Jak zaimplementować Half Adder za pomocą bramki NAND? Bramka NAND jest jednym z rodzajów bramek uniwersalnych. Wskazuje, że każdy rodzaj projektowania obwodów jest możliwy przy użyciu bramek NAND. Half Adder Z powyższego obwodu wyjście przenoszenia może być generowane przez przyłożenie wyjścia jednej bramki NAND do wejścia jako innej bramki NAND. To nic innego jak znajome dane wyjściowe uzyskane z bramki AND. Równanie wyjściowe sumy można wygenerować przez zastosowanie wyjścia początkowej bramki NAND wraz z poszczególnymi wejściami A i B do dalszych bramek NAND. Na koniec wyjścia uzyskane przez te bramki NAND są ponownie stosowane do bramki. Stąd generowane jest wyjście dla sumy. Dlatego podstawowy sumator w układzie cyfrowym można zaprojektować przy użyciu różnych bramek logicznych. Ale dodawanie wielu bitów staje się skomplikowane i uważane za ograniczenie sumatora połówkowego. Czy możesz opisać, który układ scalony jest używany do operacji inkrementacji w dowolnych praktycznych licznikach?

Half Adder Z powyższego obwodu wyjście przenoszenia może być generowane przez przyłożenie wyjścia jednej bramki NAND do wejścia jako innej bramki NAND. To nic innego jak znajome dane wyjściowe uzyskane z bramki AND. Równanie wyjściowe sumy można wygenerować przez zastosowanie wyjścia początkowej bramki NAND wraz z poszczególnymi wejściami A i B do dalszych bramek NAND. Na koniec wyjścia uzyskane przez te bramki NAND są ponownie stosowane do bramki. Stąd generowane jest wyjście dla sumy. Dlatego podstawowy sumator w układzie cyfrowym można zaprojektować przy użyciu różnych bramek logicznych. Ale dodawanie wielu bitów staje się skomplikowane i uważane za ograniczenie sumatora połówkowego. Czy możesz opisać, który układ scalony jest używany do operacji inkrementacji w dowolnych praktycznych licznikach?

Zostaw wiadomość

Lista komunikatów

Komentarze Ładowanie ...